隨著AI對更強(qiáng)大計(jì)算的需求增加,以及半導(dǎo)體行業(yè)進(jìn)入在封裝中使用多個(gè)“Chiplet”的異構(gòu)時(shí)代,封裝更加復(fù)雜和精密,對信號傳輸速度、功率傳輸、設(shè)計(jì)規(guī)則和封裝基板穩(wěn)定性的改進(jìn)將至關(guān)重要。

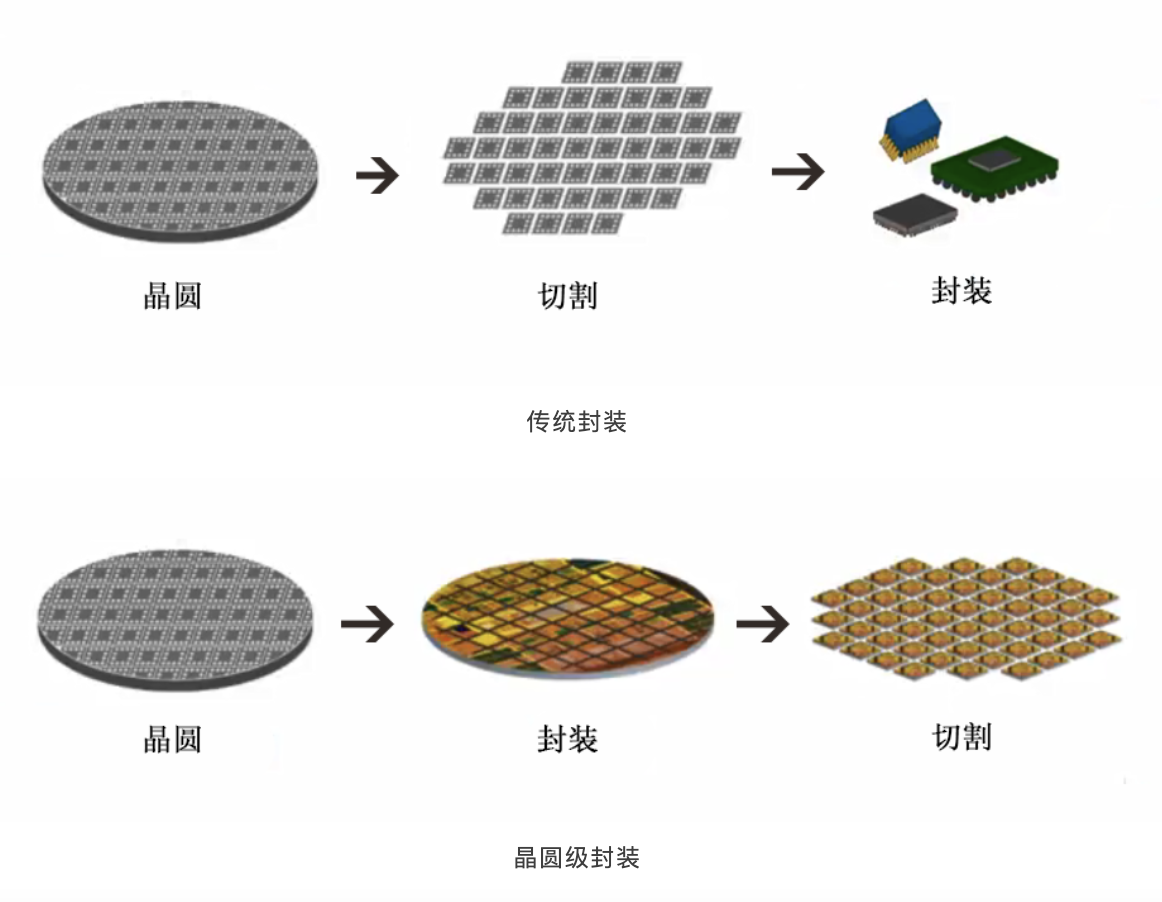

晶圓級封裝(Wafer Level Packaging,縮寫WLP)是一種先進(jìn)的封裝技術(shù),與打線型(Wire-Bond)和倒裝型(Flip-Chip)封裝技術(shù)相比 ,能省去打金屬線、外延引腳(如QFP)、基板或引線框等工序。

晶圓級封裝具有以下優(yōu)點(diǎn):

封裝尺寸小

由于沒有引線、鍵合和塑膠工藝,封裝無需向芯片外擴(kuò)展,使得WLP的封裝尺寸幾乎等于芯片尺寸。

高傳輸速度

與傳統(tǒng)金屬引線產(chǎn)品相比,WLP一般有較短的連接線路,在高速和高頻情況下,表現(xiàn)較好。

高密度連接

WLP可運(yùn)用數(shù)組式連接,芯片和電路板之間連接不限制于芯片四周,提高單位面積的連接密度。

生產(chǎn)周期短

WLP從芯片制造到、封裝到成品的整個(gè)過程中,中間環(huán)節(jié)大大減少,生產(chǎn)效率高,周期縮短很多。

工藝成本低

WLP是在硅片層面上完成封裝測試的,以批量化的生產(chǎn)方式達(dá)到成本最小化的目標(biāo)。

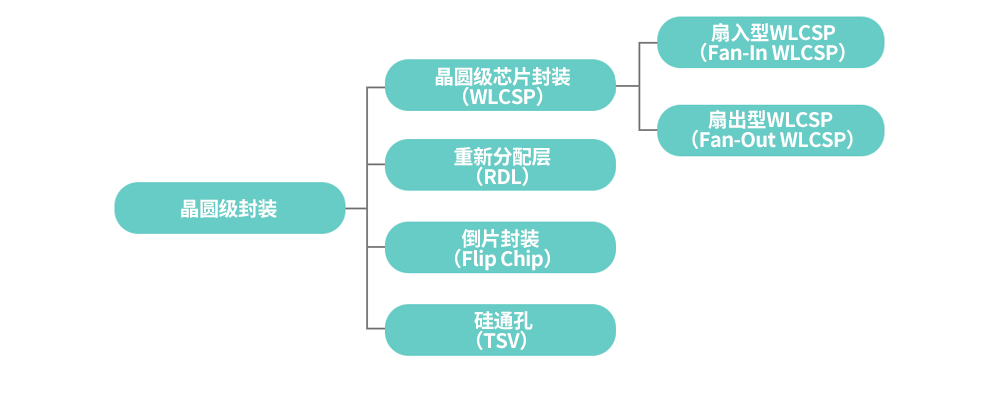

晶圓級封裝方法可分為四種不同類型:

晶圓級芯片封裝(WLCSP)

可直接在晶圓頂部形成導(dǎo)線和錫球(Solder Balls),無需基板。

重新分配層(RDL)

使用晶圓級工藝重新排列芯片上的焊盤位置1,焊盤與外部采取電氣連接方式。

倒片(Flip Chip)封裝

在晶圓上形成焊接凸點(diǎn)2進(jìn)而完成封裝工藝。

硅通孔(TSV)封裝

通過硅通孔技術(shù),在堆疊芯片內(nèi)部實(shí)現(xiàn)內(nèi)部連接。

晶圓級封裝的分類

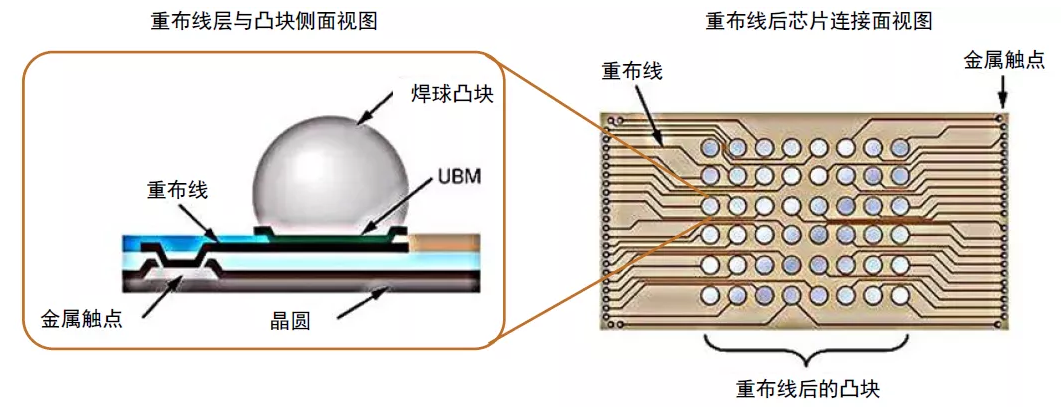

RDL的全稱是(ReDistribution Layer)重布線層,RDL重布線層作為晶圓級封裝中的核心技術(shù),起著XY平面電氣延伸和互聯(lián)的作用。RDL是將原來設(shè)計(jì)的芯片線路接點(diǎn)位置(I/O pad),通過晶圓級金屬布線制程和凸塊制程改變其接點(diǎn)位置,使芯片能適用于不同的封裝形式。

基于明陽在半導(dǎo)體領(lǐng)域的布局,先進(jìn)封裝載板與測試板進(jìn)行工藝技術(shù)研發(fā)。

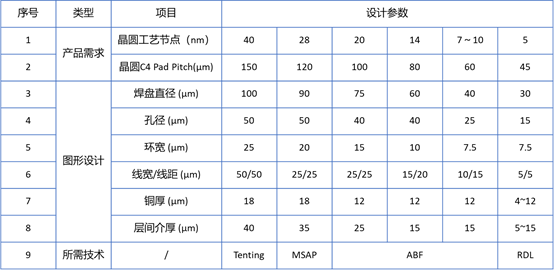

當(dāng)前工藝主要分為tenting,mSAP,SAP三種,Tenting制程由于蝕刻工藝的限制, 通常難以制作線寬/線距小于30/30μm的線路,mSAP制程的是在超薄銅箔上進(jìn)行線路銅的加厚,隨后通過閃蝕工得到完整的導(dǎo)電線路。具有制作線寬/線距小至25/25μm及以下的產(chǎn)品的能力,SAP流程與MSAP類似,但底銅更薄,可制作15/20μm的產(chǎn)品。

RDL技術(shù)可以制作更小的線路,調(diào)整陣列排布,是未來半導(dǎo)體領(lǐng)域重點(diǎn)技術(shù)之一。RDL技術(shù)相較于MSAP/SAP工藝的優(yōu)點(diǎn)是將鉆孔轉(zhuǎn)為光刻成孔,具備更高精度,可以制作更小的孔,且使用的光刻膠與PI膠的解析度高于干膜,可以制作更小的線路。

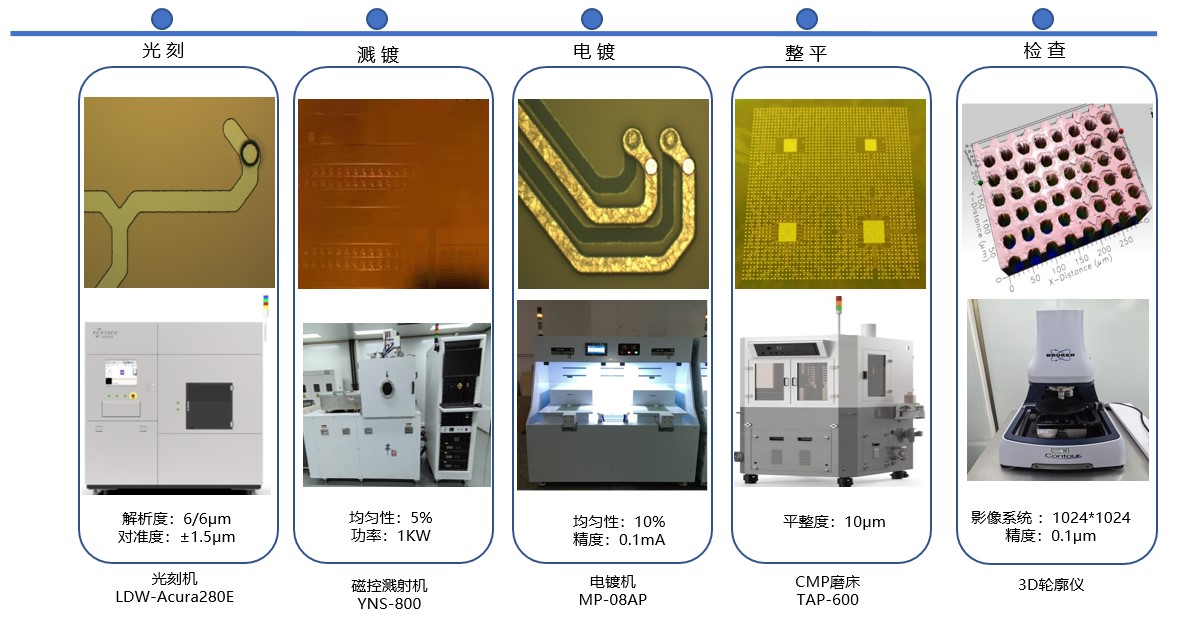

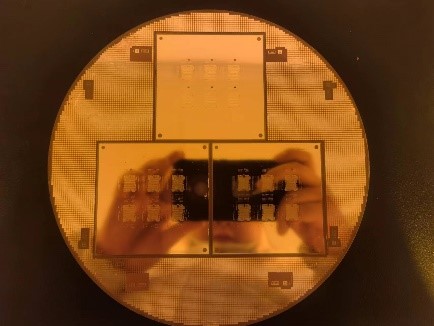

明陽中央實(shí)驗(yàn)室對RDL進(jìn)行了深入的研究,建立了一條包含磁控濺射,光刻,勻膠顯影,電鍍蝕刻的試驗(yàn)線。

當(dāng)前RDL技術(shù)已實(shí)現(xiàn)在硅基,陶瓷基,有機(jī)玻璃基板上的線路制作,可進(jìn)行銅厚6-8μm,線寬線距8/10μm的二階RDL制作,并已完成部分樣品的制作與交付。

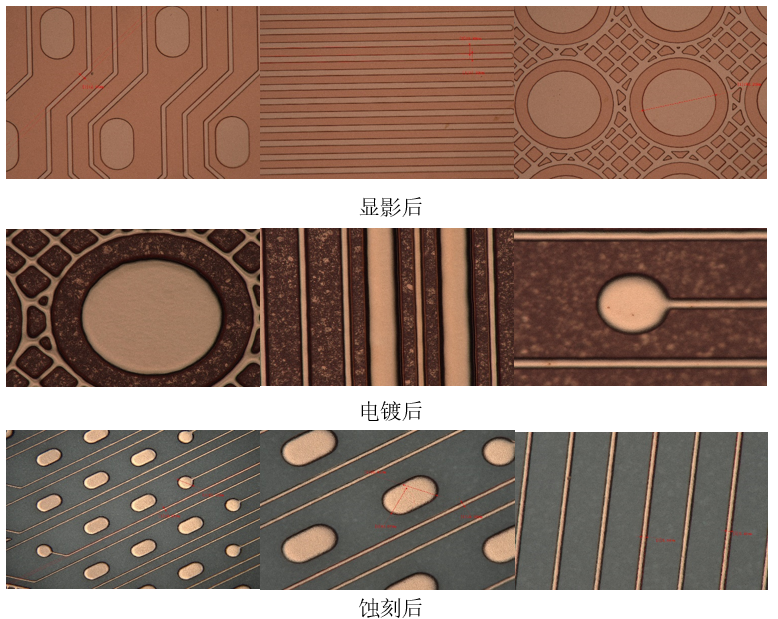

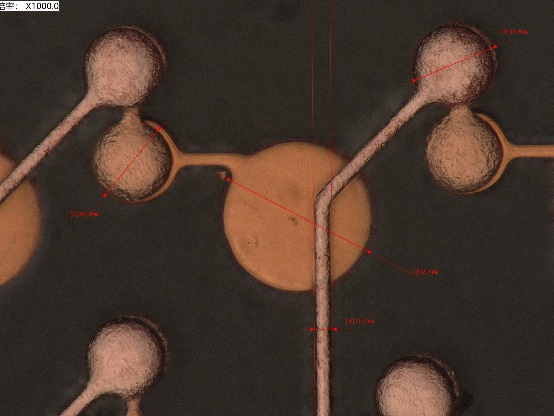

RDL工藝在顯影后,電鍍后,蝕刻后的過程圖片,線路10μm

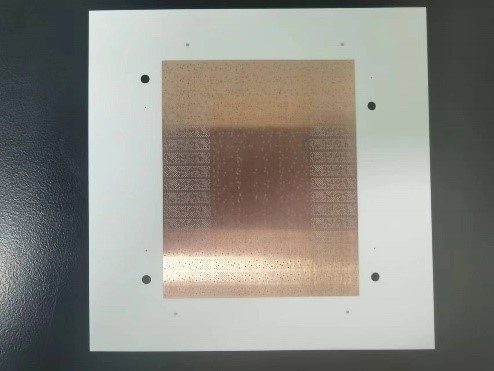

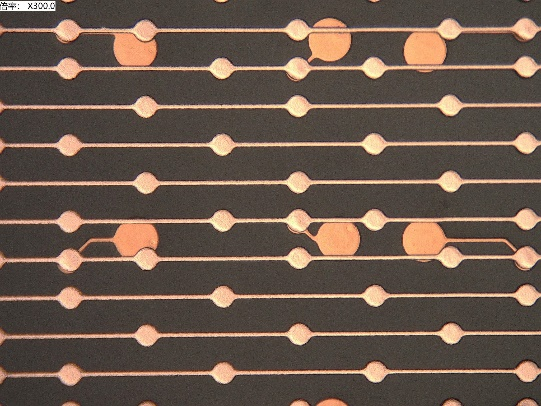

玻璃基板上的RDL,線寬線距25μm,表面處理鎳鈀金

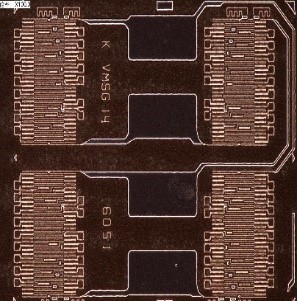

陶瓷基板上的RDL,雙面圖形,線寬線距25μm

有機(jī)基板上的RDL,線寬線距6/8μm,雙面圖形

硅基板上的RDL,線寬線距10/10μm,pitch 85μm

玻璃基板上的三階RDL,線寬線距10/10μm,pitch 85μm